-

Scaling Machine Learning Performance with Moore's Law

Thu, Sep 28, 2017 @ 02:00 PM - 03:15 PM

Ming Hsieh Department of Electrical and Computer Engineering

Conferences, Lectures, & Seminars

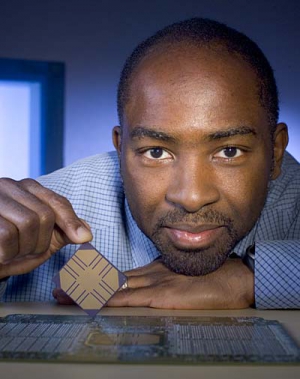

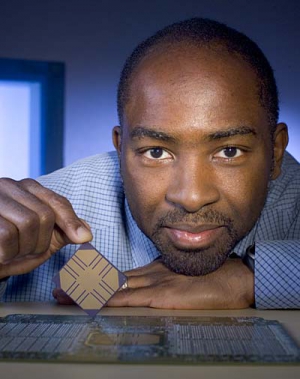

Speaker: Kunle Olukotun, Stanford University

Talk Title: Scaling Machine Learning Performance with Moore's Law

Abstract: The computational demands of machine learning (ML) requires energy efficient machine learning specific accelerators. This naturally results in heterogeneous computing platforms composed of CPUs and ML Accelerators. However, the staggering cost (the majority of the cost is for software development) of designing custom integrated circuits for many application domains makes it cost-prohibitive to design these accelerators. This situation calls for a new paradigm for designing accelerators that can provide energy-efficient ML-specific performance and easier software development. The key to this new paradigm is to enable application developers to optimize the underlying hardware to make it specific to their ML application needs. The new design paradigm consists of new application ML-specific programing languages, new machine learning algorithms, new compilation technology to target both existing (FPGAs) and new (Software Defined Hardware) reconfigurable architectures.

Biography: Kunle Olukotun is the Cadence Design Systems Professor of Electrical Engineering and Computer Science at Stanford University. Olukotun is well known as a pioneer in multicore processor design and the leader of the Stanford Hydra chip multipocessor (CMP) research project. Olukotun founded Afara Websystems to develop high-throughput, low-power multicore processors for server systems. The Afara multicore processor, called Niagara, was acquired by Sun Microsystems. Niagara derived processors now power all Oracle SPARC-based servers. Olukotun currently directs the Stanford Pervasive Parallelism Lab (PPL), which seeks to proliferate the use of heterogeneous parallelism in all application areas using Domain Specific Languages (DSLs). Olukotun is a member of the Data Analytics for What's Next (DAWN) Lab which is developing infrastructure for usable machine learning. Olukotun is an ACM Fellow and IEEE Fellow for contributions to multiprocessors on a chip and multi-threaded processor design. Olukotun received his Ph.D. in Computer Engineering from The University of Michigan.

Host: Xuehai Qian, x04459, xuehai.qian@usc.edu

Location: Hughes Aircraft Electrical Engineering Center (EEB) - 132

Audiences: Everyone Is Invited

Contact: Gerrielyn Ramos

This event is open to all eligible individuals. USC Viterbi operates all of its activities consistent with the University's Notice of Non-Discrimination. Eligibility is not determined based on race, sex, ethnicity, sexual orientation, or any other prohibited factor.